# F1E21

# **Databook**

Confidential / Preliminary Documentation

Revision 1.0

Copyright© 2006 F1BT Corp.

# List of Contents

- 1 General

- 1.1 Overview

- 1.2 Features

- 1.3 Application

- 1.4 Pinout Diagram & Outline Size

- 1.5 Device Terminal Descriptions

- 1.6 Package Dimensions

- 2 Characteristics

- 2.1 Electrical Characteristics

- 2.2 Radio Characteristics

- 3 Terminal Description

- 3.1 UART

- 3.1.1 UART Setting

- 3.1.2 UART Bypass Mode

- 3.2 USB

- 3.3 I<sup>2</sup>C

- 3.4 Audio PCM interface

- 3.4.1 PCM Configuration

- 4 Boot Interface configures

- 5 Application Schematic

- 6 Revision History

### 1. General

#### 1.1 overview

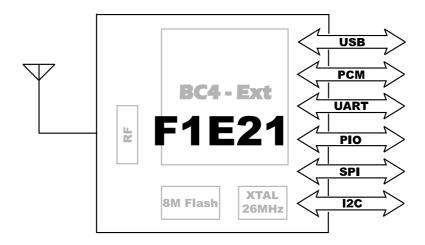

This specification covers Bluetooth module (class-2) which complies with Bluetooth specification version 2.0 + EDR and integrates RF & Baseband controller in small package. This Module has deployed CSR's BC04-External chipset.

All detailed specification including pinouts and electrical specification may be changed without notice.

### **Overview F1E21**

### 1.2 Features

- Fully Qualified Bluetooth v2.0 + EDR

- Enhanced Data Rate (EDR) compliant with v2.0.E.2 of specification for both 2Mbps and 3Mbps modulation modes

- Full-speed Bluetooth Operation with Full Piconet Support

- Scatternet Support

- Low Power Consumption

- Support for 802.11 Co-existence

- RoHS Compliant

- USB and Dual UART Ports

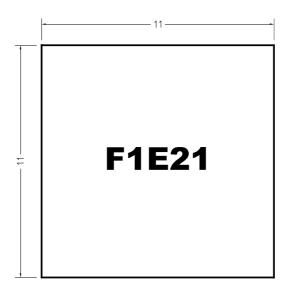

- Competitive Size (11mm x 11mm x 1.56mm : QFN 36Pin)

## 1.3 Application

- Notebook PC, Desktop PC

- PDA

- Cordless headset

- Digital camera & printer

- GPS,POS, Barcode Reader

- Domestic and industrial applications

- Access Point

- Serial Adapter

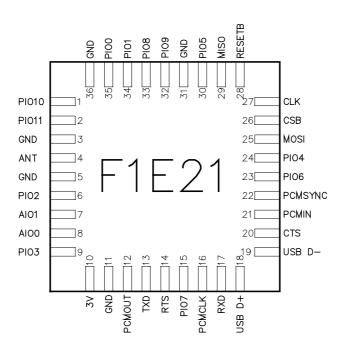

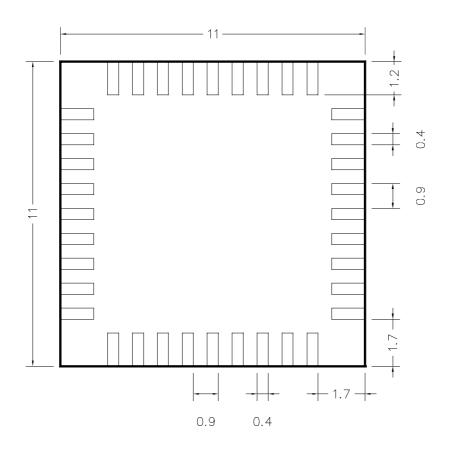

# 1.4 Pinout Diagram & Outline Size

# **F1E21 Pinout Diagram**

F1E21 Size

### 1.5 Device Terminal Functions

|            | PIN      | Name         | Description                                              |

|------------|----------|--------------|----------------------------------------------------------|

|            | PCM OUT  | 12           | Synchronous data output                                  |

| PCM        | PCM IN   | 21           | Synchronous data input                                   |

| 1 0101     | PCM CLK  | 16           | Synchronous data clock                                   |

|            | PCM SYNC | 22           | Synchronous data sync                                    |

|            | TXD      | 13           | UART data output, active low                             |

| LLADT      | RXD      | 17           | UART data input, active low (idle status high)           |

| UART       | CTS      | 20           |                                                          |

|            | RTS      | 14           |                                                          |

|            | USB -    | 19           | USB -                                                    |

| USB        | USB +    | 18           | USB + with selectable internal 1.5k pull-up resistor     |

|            | PIO0     | 35           |                                                          |

|            | PIO1     | 34           |                                                          |

|            | PIO2     | 6            |                                                          |

|            | PIO3     | 9            |                                                          |

|            | PIO4     | 24           |                                                          |

|            | PIO5     | 30           | Programmable input/output line                           |

|            | PIO6     | 23           |                                                          |

| PIO & AIO  | PIO7     | 15           | PIO 4,5,6,7 Can be used UART bypass mode                 |

|            | PIO8     | 33           |                                                          |

|            | PIO9     | 32           | PIO 6,7,8 Can be used to form I2C interface              |

|            | PIO10    | 1            |                                                          |

|            | PIO11    | 2            |                                                          |

|            | AIO0     | 8            |                                                          |

|            | AIO1     | 7            |                                                          |

|            | SPI MOSI | 25           | Serial Peripheral Interface data input                   |

|            | SPI CLK  | 27           | Serial Peripheral Interface clock                        |

| SPI        | SPI MISO | 29           | Serial Peripheral Interface data output                  |

|            | SPI CSB  | 26           | Chip Select for Synchronous SPI active low               |

|            | ANT      | 4            | RF Connection to Antenna                                 |

|            | GND      | 3,5,11,31,36 | Ground                                                   |

| Other Pins | 3V       | 10           | Main supply input voltage.                               |

|            | RESETB   | 28           | Reset if low. Input debounced so must be low for >5ms to |

|            |          |              | cause a reset                                            |

|            |          |              | cause a reset                                            |

### 1.6 Module Dimension

### 2. Characteristics

### 2.1 Electrical Characteristics

| Absolute Maximum Ratings |          |          |  |  |  |

|--------------------------|----------|----------|--|--|--|

| Rating                   | Minimum  | Maximun  |  |  |  |

| Storage temperature      | -40°C    | 85°C     |  |  |  |

| Supply voltage : VCC     | -0.4V    | 3.7V     |  |  |  |

| Other terminal voltages  | VSS-0.4V | VCC+0.4V |  |  |  |

| Recommended Operating Conditions    |      |  |  |  |  |

|-------------------------------------|------|--|--|--|--|

| Operating Condition Minimum Maximun |      |  |  |  |  |

| Operating temperature range         | 70°C |  |  |  |  |

| Supply voltage: VCC 1.7V 3.6V       |      |  |  |  |  |

### 2.2 RF Characteristics

#### **Transmitter**

| Specification                        | Condition                                                         | Min               | Тур | Max               | Unit            |

|--------------------------------------|-------------------------------------------------------------------|-------------------|-----|-------------------|-----------------|

| Output transmit power                | Normal                                                            | -6                | 1   | 4                 | dBm             |

| Transmit power density               | Normal                                                            |                   |     | 4                 | dBm             |

| Transmit power control               | Normal                                                            | 2                 |     | 8                 | dBm             |

| Frequency Range                      | Normal                                                            | 2400              |     | 2483.5            | MHz             |

| 20dB bandwidth for modulated carrier | Normal                                                            |                   | 850 | 1000              | KHz             |

| Adjacent channel transmit power      | ±2MHz<br>±3MHz<br>±4MHz                                           |                   |     | -20<br>-40<br>-40 | dBm             |

| Modulation Characteristics           | f1avg<br>f2max<br>f2avg / f1avg                                   | 140<br>115        |     | 175<br>80         | KHz<br>KHz<br>% |

| Initial carrier frequency tolerance  | Normal                                                            | -20               |     | 20                | KHz             |

| Carrier frequency Drift              | One slot packet(DH1) Three slot packet(DH3) Five slot packet(DH5) | -25<br>-40<br>-40 |     | 25<br>40<br>40    | KHz             |

#### **Transceiver**

| Specification                   | Condition      | Min | Тур | Max | Unit  |

|---------------------------------|----------------|-----|-----|-----|-------|

|                                 | 30MHz ~ 1GHz   |     |     | -36 |       |

| Adjacent channel transmit power | 1GHz ~12.75GHz |     |     | -30 | dBm   |

|                                 | 1.8GHz ~5.1GHz |     |     | -47 | ubili |

|                                 | 5.1GHz ~5.3GHz |     |     | -47 |       |

|                                 |                |     |     |     |       |

#### **Receiver**

| Specification                | Condition                                                                                           | Min                      | Тур | Max                   | Unit |

|------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------|-----|-----------------------|------|

| Sensitivity level (0.1% BER) | Single slot packets                                                                                 | -70                      | -80 |                       | dBm  |

| Transmit power density       | Multi slot packet                                                                                   | -70                      | -80 |                       | dBm  |

| C/I performance              | co-channel<br>1MHz (Adjacent channel)<br>2MHz (2nd Adjacent channel)<br>3MHz (3rd Adjacent channel) |                          |     | 11<br>0<br>-30<br>-40 | dB   |

| Blocking performance         | 30MHz ~ 2000MHz<br>2000MHz ~ 2400MHz<br>2500MHz ~ 3000MHz<br>3000MHz ~ 12.75GHz                     | -10<br>-27<br>-27<br>-10 |     |                       | dBm  |

| Intermodulation performance  | n=5                                                                                                 | -39                      |     |                       | dBm  |

| Maximum input level          |                                                                                                     | -20                      | -10 |                       | dBm  |

### 3. Terminal Description

#### **3.1 UART**

Four signals are used to implement the UART function.

UART\_TXD and UART\_RXD transfer data between the two devices.

#### 3.1.1 UART Setting

User can change data format the following selection using PSKEY.

However, host shall communicate with default setting UART connection initiated at first time.

Baud Rate = (PSKEY UART BAUD RATE) / 0.004096

| Parameter           | Possible value    |  |

|---------------------|-------------------|--|

| Baud Rate           | 9600 ~ 3M Baud    |  |

| Flow Control        | None              |  |

| Parity              | None, Odd or Even |  |

| Number of Stop Bits | 1 or 2            |  |

| Bits per channel    | 8                 |  |

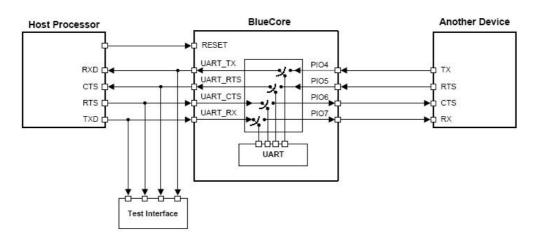

#### 3.1.2 UART Bypass Mode

In order to apply the UART bypass mode, a BCCMD command will be issued to F1E21 upon this, it will switch the bypass to PIO4,5,6,7 as shown in figure. When the bypass mode has been invoked, module enters the deep sleep state indefinitely

#### **3.2 USB**

BlueCore4 - External devices contain a full speed (12Mbits/s) USB interface that is capable of driving a USB cable directly. No external USB transceiver is required. The device operates as a USB peripheral, responding to requests from a master host controller such as a PC. Both the OHCI and the UHCI standards are supported. The set of USB endpoints implemented can behave as specified in the USB section of the Bluetooth specification v1.2 or alternatively can appear as a set of endpoints appropriate to USB audio devices such as speakers.

As USB is a Master/slave oriented system (in common with other USB peripherals), BlueCore3-Multimedia External only supports USB slave operation.

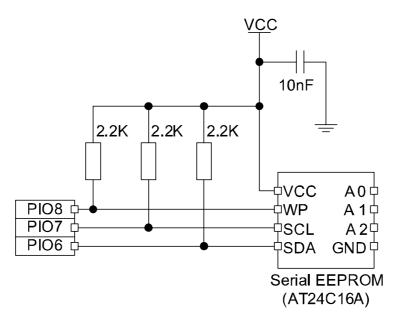

#### 3.3 I2C

PIO[8:6] can be used to form an interface. The interface is driven by "bit banging" these PIO pins using software. Therefore it is suited only to relatively slow functions such as driving a dot matrix liquid crystal display (LCD).

Note. PIO[7:6] dual functions, UART bypass and EEPROM support, therefore devices using an EEPROM connect support UART bypass mode. PIO Lines need to be pulled-up through 2.2K

#### 3.4 PCM

Pulse Code Modulation (PCM) is a standard method used to digitize audio (particularly voice) patterns for transmission over digital communication channels. Through its PCM interface, this module has hardware support for continual transmission and reception of PCM data, so reducing processor overhead for wireless headset applications. This module offers a bi-directional digital audio interface that route directly into the baseband lauer of the on-chip firmware. It dose not pass through the HCI protocol layer.

Hardware allows the data to be sent to and received from a SCO connection. This module interfaces directly to PCM audio devices including the following:

- Qualcomm MSM 3000 series and MSM 5000 series CDMA baseband devices

- OKI MSM7705 for channel A-law and u-law CODEC

- Motorola MC145481 8-bit A-law and u-law CODEC

- Motorola MC145483 13-bit linear CODEC

- STW 5093 and 5094 14-bit linear CODECs

#### 3.4.1 PCM Configuration

The PCM configuration is set using two PS keys, PSKEY\_PCM\_CONFIG32 and PSKEY\_PCM\_LOW\_JITTER\_CONFIG. The default for long frame sync and interface master generating 256KHz PCM\_CLK with no tri-state of PCM\_OUT.

| Parameter    | Possible value                           |  |

|--------------|------------------------------------------|--|

| Mode         | Slave, Master                            |  |

| Clock rate   | Master Mode : 128, 256, 512KHz           |  |

| Clock rate   | Slave Mode : up to 2048KHz               |  |

| Sync formats | Long frame sync, Short frame sync        |  |

| Data formats | 13 or 16bit linear, 8-bit A-law to u-law |  |

# 4. Revision History

| Revision | Date       | Change Descriptions | Issued by |

|----------|------------|---------------------|-----------|

| Rev 1.0  | 2006-12-21 | Initial release     | Narsen    |

|          |            |                     |           |

|          |            |                     |           |

|          |            |                     |           |

|          |            |                     |           |

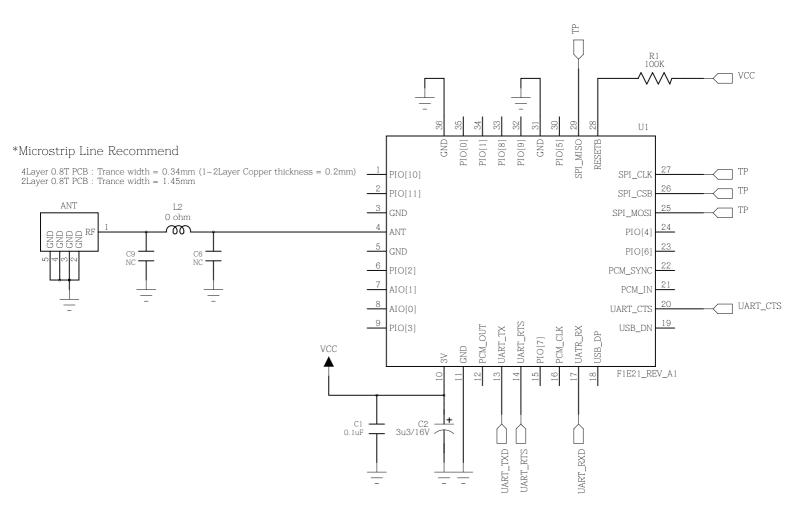

# 5. Application Schematic